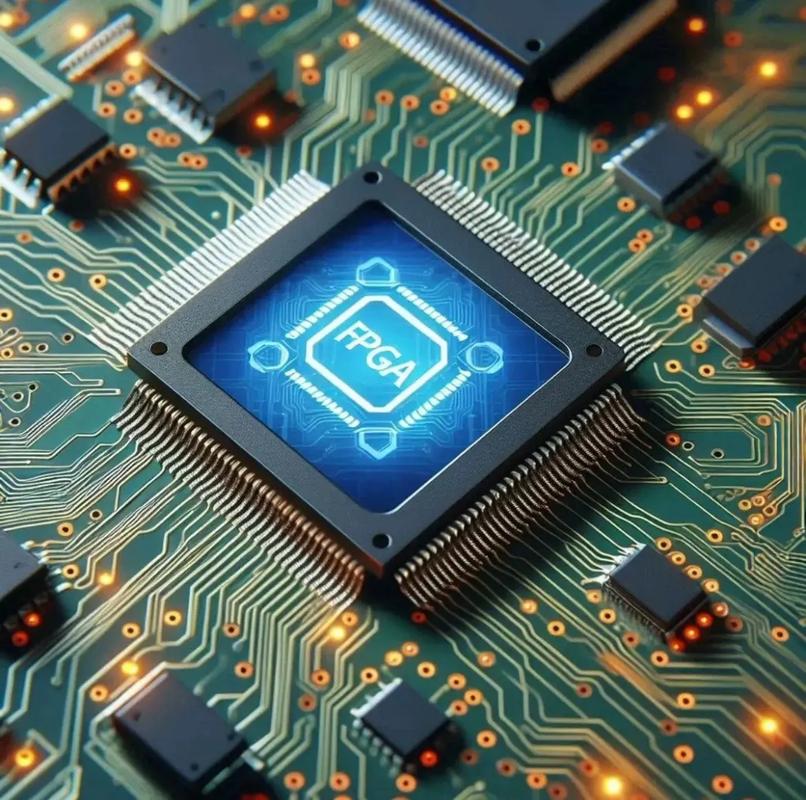

什么是FPGA?为什么用它来实现AI?

FPGA (Field-Programmable Gate Array),即现场可编程门阵列,是一种半定制化的集成电路芯片。

- 核心特点:

- 可编程性:与无法修改的ASIC(专用集成电路)不同,FPGA可以在出厂后由用户或开发者通过硬件描述语言(如Verilog, VHDL)或高级综合工具重新配置其内部逻辑结构。

- 并行性:FPGA的硬件架构本质上是并行的,你可以同时配置成千上万个独立的计算单元(查找表LUT、寄存器等)来执行不同的任务,这对于AI中大量重复的矩阵运算(如卷积、矩阵乘法)来说是天然的优势。

- 低延迟:AI算法在FPGA上被直接“硬化”为硬件电路,数据流直接在硬件中处理,无需像CPU/GPU那样经过取指、译码、发射等复杂的指令集流程,这使得FPGA可以实现极低的推理延迟。

- 高能效比:FPGA只执行当前任务所需的硬件电路,没有多余的功耗单元,对于特定的AI任务,其能效比通常远高于通用处理器。

- 硬件在环:FPGA可以与传感器、执行器等外部硬件直接连接,实现高速的实时数据处理和闭环控制,这在自动驾驶、工业控制等场景中至关重要。

CPU/GPU是通用的冯·诺依曼架构,通过软件指令来计算;而FPGA是为特定任务定制的硬件架构,通过硬件电路来计算,对于AI推理这种计算密集、模式固定的任务,FPGA能提供“量身定制”的高效解决方案。

AI在FPGA上实现的关键技术流程

将一个AI模型(通常是神经网络)部署到FPGA上,不是简单地把代码烧进去,而是一个复杂的软硬件协同设计过程。

第一步:模型选择与优化

并非所有AI模型都适合在FPGA上实现,FPGA最适合那些计算模式固定、对延迟敏感的模型,尤其是卷积神经网络。

- 模型选择:YOLO、SSD等目标检测模型,MobileNet、ShuffleNet等轻量级分类模型是FPGA上的常见应用。

- 模型优化:

- 量化:这是最关键的一步,将模型中的32位浮点数运算转换为16位、8位甚至4位的整数运算,这能极大地减少模型大小、内存占用和计算量,非常适合FPGA的定点运算单元。

- 剪枝:移除神经网络中冗余的连接或神经元,使模型结构更稀疏,便于硬件实现稀疏计算。

- 知识蒸馏:用一个大的、高精度的“教师模型”来训练一个小型的“学生模型”,让学生模型在保持较高精度的同时,结构更简单,更适合部署。

第二步:硬件架构设计

这是将优化后的AI算法映射到FPGA硬件核心的步骤。

- 数据流架构:根据神经网络的计算图,设计硬件上的数据流动方式,常见的有:

- 脉动阵列:特别适合矩阵乘法和卷积运算,数据像血液一样在阵列中“脉动”流过,每个处理单元只做最简单的乘加运算,效率极高。

- 流水线:将一个复杂的计算任务(如一层卷积)拆分成多个阶段,每个阶段由一个独立的硬件模块处理,数据像在流水线上一样,连续不断地被处理,大大提高了吞吐率。

- 并行化设计:充分利用FPGA的并行资源。

- 层内并行:为同一层的不同计算任务(如图像的不同区域)分配多个并行的计算单元。

- 层间并行:为网络的不同层分配独立的计算单元,实现流水线式的处理。

第三步:高层次综合

这是近年来FPGA开发的一大趋势,极大地降低了AI部署的门槛。

- 传统方法:开发者用Verilog/VHDL编写底层的门级电路代码,工作量大、周期长、门槛高。

- HLS方法:开发者用C/C++/Python等高级语言描述算法的行为和规则(如循环、函数调用),然后HLS工具会自动将这些描述综合成可配置的FPGA硬件电路。

- 优势:大大缩短了开发周期,让算法工程师也能参与到FPGA的硬件设计中,专注于算法优化而非底层电路细节。

第四步:部署与验证

- 工具链:使用Xilinx (AMD) 的Vitis AI、Intel的OpenVINO™ Toolkit等工具,它们提供了从模型优化、HLS到最终比特流生成的完整流程。

- 验证:在FPGA板上运行部署好的模型,使用测试数据集验证其准确性和性能(如FPS、延迟、功耗),确保满足应用需求。

FPGA vs. GPU vs. CPU 实现AI的对比

| 特性 | FPGA | GPU | CPU |

|---|---|---|---|

| 架构类型 | 硬件可编程,并行电路 | 大规模并行多核 | 通用串行/多核 |

| 灵活性 | 高:可针对不同算法重新配置硬件 | 中:通过软件编程,但硬件固定 | 高:通用软件编程 |

| 性能/吞吐量 | 针对特定任务极高 | 非常高:通用并行计算之王 | 低 |

| 延迟 | 极低 (纳秒级) | 低 (微秒级) | 高 (毫秒级) |

| 能效比 | 极高 (针对特定任务) | 高 | 低 |

| 开发难度/周期 | 高,需要硬件设计知识 | 中,成熟的CUDA/ROCm生态 | 低,最简单的编程模型 |

| 成本 | 高端芯片单价高,但NRE(一次性工程费)低 | 中等 | 低 |

| 主要应用场景 | 低延迟、高能效、实时嵌入式系统:自动驾驶、工业视觉、无人机、金融高频交易 | 通用AI训练和大规模推理:云端数据中心、科学研究 | 非实时、通用计算:数据预处理、后处理、小规模推理 |

典型应用场景

-

自动驾驶与高级驾驶辅助系统:

- 需求:实时处理摄像头、雷达数据,进行物体检测、车道线识别,延迟要求极低(毫秒级),且车辆对功耗和成本敏感。

- FPGA优势:提供极低的推理延迟和极高的能效比,满足车规级的实时性和可靠性要求。

-

工业自动化与机器视觉:

- 需求:在生产线上进行产品缺陷检测、尺寸测量、分拣等,需要在设备端实时完成,不能依赖云端。

- FPGA优势:FPGA可以直接与工业相机、传感器连接,实现“硬件在环”的实时闭环控制,提高生产效率和精度。

-

数据中心与边缘计算:

(图片来源网络,侵删)

(图片来源网络,侵删)- 需求:在数据中心内,FPGA可以作为智能网卡或加速卡,卸载虚拟化、网络包处理、特定AI推理任务,提升服务器整体效率,在边缘侧(如基站、智能摄像头),FPGA能在本地完成AI计算,减少数据上传带宽,保护隐私。

-

航空航天与国防:

- 需求:卫星、无人机等平台对功耗、重量、散热和可靠性有严苛要求,同时需要强大的机载AI处理能力。

- FPGA优势:其高可靠性、可重构性和高能效比使其成为这些极端环境下的理想选择。

挑战与未来趋势

挑战:

- 开发门槛高:需要同时具备AI算法和数字电路设计知识的复合型人才。

- 工具链成熟度:虽然HLS在进步,但相比GPU的成熟生态,FPGA的工具链和库仍有提升空间。

- 成本:高性能FPGA芯片本身价格不菲。

未来趋势:

- AI与FPGA的深度融合:像AMD/Xilinx收购赛灵思后推出的“自适应SoC”,将强大的Arm CPU核心与FPGA逻辑集成在单一芯片上,实现了软硬件的完美协同,成为业界主流方向。

- 云化FPGA服务:亚马逊AWS、微软Azure、阿里云等云厂商都提供了FPGA实例,用户可以按需租用FPGA的计算能力,大大降低了使用门槛。

- 更智能的编译器与工具:未来的HLS工具将更加智能,能自动将高级AI模型(如Transformer)映射到最优的FPGA硬件架构,实现“一键部署”。

- 存算一体:突破传统冯·诺依曼架构中“内存墙”的限制,在存储单元内部直接进行计算,进一步提升能效和性能,这是FPGA和AI结合的下一个前沿方向。

人工智能在FPGA上的实现,是一种为特定AI任务定制硬件的优化方法,它通过牺牲一定的通用性,换取了极致的低延迟、高能效和灵活性,虽然开发难度较高,但随着自适应SoC、云服务和HLS工具的普及,FPGA正在成为AI从云端走向边缘、从通用走向专用、从研究走向部署的关键使能技术,在自动驾驶、工业4.0、智慧城市等领域扮演着越来越重要的角色。

标签: FPGA人工智能加速实现 基于FPGA的人工智能开发 人工智能FPGA硬件实现